#### International Journal of

## INTELLIGENT SYSTEMS AND APPLICATIONS IN **ENGINEERING**

ISSN:2147-6799 www.ijisae.org

# Design and Simulation of 8-Bits Arithmetic Logic Unit (ALU) For **Inverter Applications**

Vijay Kumar Ram, Rahul Prakash, Vijay Singh, Yogesh Kumar, Parul Varshney, Sachin Kumar

Submitted: 28/01/2024 Revised: 07/03/2024 Accepted: 22/03/2024

Abstract — In this paper, an 8-bit ALU (Arithmetic Logic Unit) for 3V operation has been designed. Numerous mathematical and logical operations can be carried out using the ALU. The central processing unit (CPU), memory unit, and input/output unit are the fundamental components of a computer. The CPU of a computer is essentially the same as a human brain. The ALU, control unit, and all of the registers are included. All design were simulated using Tanner EDA tool v12.5 in 32nm 0.5 technology. Performance analyses were done with respect to power, delay and power delay product.

Keywords— Inverter, Full Subtractor, Multiplexer Tanner Tool V\_12.5.

#### Introduction

Functionally, an ALU can be divided up into three circuits: the arithmetic circuit, the logic circuit and the shift circuit[1]. i)The arithmetic circuit performs typical arithmetic operations such as addition, subtraction and increment or decrement by one [2]. The basic component of an arithmetic circuit is the Full adder. By using a multiplexer to control the data inputs to the adder [3], it is possible to obtain different types of arithmetic operations [4-7]. Depending on the selection inputs and the input carry, the arithmetic circuit can generate [8]. the different arithmetic micro-operations listed Table 1.

**Original Research Paper**

| - I |    |     |      |        |                 |  |  |

|-----|----|-----|------|--------|-----------------|--|--|

| S   | S0 | Cin | Inpu | Output | Micro operation |  |  |

| 1   |    |     | t    |        |                 |  |  |

| 0   | 0  | 0   | В    | A+B    | Add             |  |  |

| 0   | 0  | 1   | В    | A+B+1  | Add with cry    |  |  |

| 0   | 1  | 0   | B'   | A+B'   | Sub with borrow |  |  |

| 0   | 1  | 1   | B'   | A-B    | Sub             |  |  |

| 1   | 0  | 0   | 0    | A      | Transfer A      |  |  |

| 1   | 0  | 1   | 0    | A+1    | Increment by 1  |  |  |

| 1   | 1  | 0   | 1    | A-1    | Decrement A by1 |  |  |

| 1   | 1  | 1   | 1    | A      | Transfer A      |  |  |

|     |    |     |      |        |                 |  |  |

|     |    |     |      |        |                 |  |  |

**Table 1:** Function table of the arithmetic Circuit

ii) The ALU, logic circuit performs the basic logic microoperations: NOT, AND, OR and XOR. From these four micro-operations all known logic micro-operations can be derived. Figure 5-2 shows the logic diagram for one stage of logic circuit. The four gates generate the four logic operations and the multiplexer select the desired operation as shown in Table 2.

| S1 | S0 | Output | Operation  |  |

|----|----|--------|------------|--|

| 0  | 0  | AB     | AND        |  |

| 0  | 1  | A+B    | OR         |  |

| 1  | 0  | A⊕B    | XOR        |  |

| 1  | 1  | A'     | Complement |  |

Table 2: Function table of the 2-bit Logic Circuit.

iii) Shift circuit used to perform the shift micro-operations. The contents of a register can be shifted serially to the left or to the right. The shift circuit contains multiplexers as shown in Figure 5-3. when the select line is 0 the 4-bit input data

Department of ECE, SCRIET, CCS University, Meerut, Uttar Pradesh. vijayk10ster@gmail.com

Department of EIE, SCRIET, CCS University, Meerut, Uttar Pradesh. coolrahul2287@gmail.com

Department of EIE, SCRIET, CCS University, Meerut, Uttar Pradesh. scrietvijay2010@gmail.com

Department of ME, SCRIET, CCS University, Meerut, Uttar Pradesh. yogeshyogi7916@gmail.com

Department of ECE, SCRIET, CCS University, Meerut, Uttar Pradesh. parulspsvarshney@gmail.com

Department of AS, SCRIET, CCS University, Meerut, Uttar Pradesh. Sachin10phy@gmail.com

are shifted right. When the select line is 1 the input data are shifted left. There are two serial inputs one for shift left and other one for shift right. The function Table 3 shows the outputs of the multiplexers in each case.

| S | Н3 |    |    |    |  |  |

|---|----|----|----|----|--|--|

|   | Н3 | H2 | H1 | Н0 |  |  |

| 0 | IR | A3 | A2 | A1 |  |  |

| 1 | A2 | A1 | A0 | IL |  |  |

Table 3: Function table of the 4-bit Shift Circuit

#### **Block Diagram for Designing of ALU**

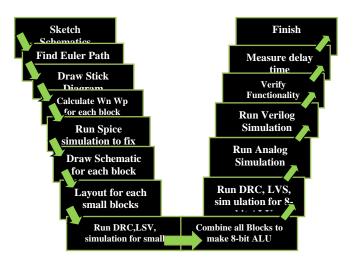

ALU design by following the correct procedure some introductory part is given as, Making the programming, draw the schematic diagram, and for the layout diagram at each and every step check the DRC for the proper designing. The design of the 8-bit ALU is based on the use of a carry select line, implemented using AMI's C5N process. Once verification was completed parasitic were extracted. To create a test for finding the maximum operating frequency a pseudo-random input stream was applied to each input of the ALU and observed the circuit during the input transition. If the switching of the transistors takes longer than the period of the input then the ALU may give a erroneous output. Fig 1 shows the step-by-step procedure for the ALU designing.

Fig1: Block Diagram of ALU Design

#### **MODULE**

There are different modules use for the designing of the ALU, schematic and waveform (DC and AC Analysis) some of them are as follows.

#### **Simulation and Results**

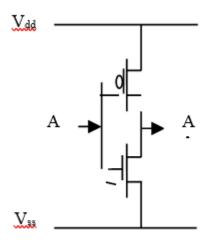

## I) Inverter

An inverter or NOT gate is a logic gate which an inverter circuit outputs a voltage representing the opposite logiclevel to its input. Inverters can be constructed using a single NMOS transistor or a single PMOS transistor coupled with a resistor. Since this 'resistive-drain' approach uses only a single type of transistor, it can be fabricated at low cost. However, because current flows through the resistor in one of the two states, the resistive-drain configuration is disadvantaged for power consumption and processing speed implements logical negative.

The truth table is shown in **table 2.**

Fig.2: Structure of inverter.

| OUTPUT |  |  |

|--------|--|--|

| NOT A  |  |  |

| 0      |  |  |

| 1      |  |  |

|        |  |  |

**Table 2**. Truth table of inverter.

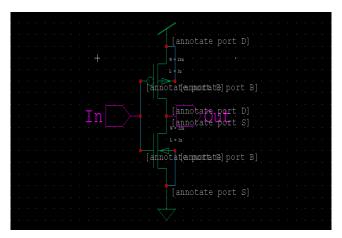

Fig.3 Schematic diagram of Inverter.

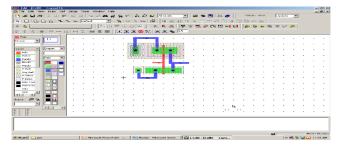

Fig. 4 Layout of Inverter.

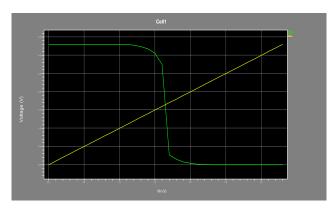

Fig. 5 DC analysis of Inverter.

Fig. 6 AC analysis of Inverter.

## II) Full\_ Adder

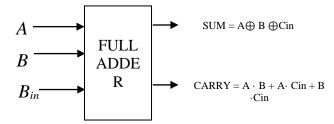

In ALU, full adder forms the core of the entire design. The full adder performs the computing function of the ALU. A full adder could be defined as a combinational circuit that forms the arithmetic sum of three input bits. It consists of three inputs and two outputs. In our design, we have designated the three inputs as A, B and Cin. The third input Cin represents carry input to the first stage. The outputs are SUM and CARRY [9-10]. Figure 7 shows the logic level diagram of a full adder. The Boolean expressions for the SUM and CARRY bits are as shown below.

$SUM = A \oplus B \oplus Cin$

$CARRY = A \cdot B + A \cdot Cin + B \cdot Cin$

Fig. 7 Block diagram of Full\_ Adder.

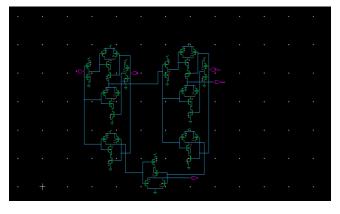

Fig. 8 Schematic diagram of Full\_Adder.

## III) Full Subtractor

Full Subtractor is a combinational circuit with three inputs A, B and  $B_{in \text{ and}}$  two outputs Difference(D) and Borrow (B<sub>0</sub>) [13].

$D = A \oplus B \oplus B_{in}$   $B_0 = A'B_{in} + A'B + BB_{in}$   $A \longrightarrow FULL$   $B \longrightarrow SUBT$  RACT RACT  $OR \longrightarrow B_0 = A'B_{in} + A'B + BB_{in}$

Fig. 9 Block diagram of Full\_Subtractor

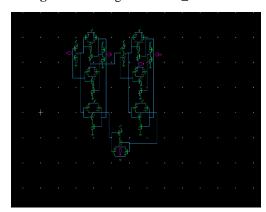

Fig. 10 Schematic diagram of Full Subtractor.

## IV) Multiplexer

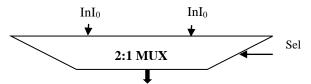

**Multiplexer** (or **MUX**) is a device that selects one of several analog or digital input signals and forwards the selected input into a single line.  $^{1}$  A multiplexer of  $2^{n}$  inputs has n select lines, which are used to select[11].

Fig. 11 Block of 2:1 MUX

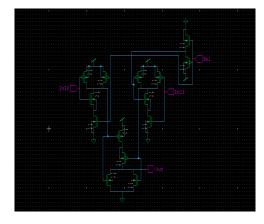

Fig.12 Schematic diagram of Multiplexer\_21.

Fig. 13 DC analysis of Multiplexer\_21.

## V) Arithmetic Logic Unit

A 8-bit ALU has been designed for 3V operation. The ALU can perform various arithmetic and logical operations. The basic blocks of a computer are central processing unit (CPU), memory unit, and input/output unit. CPU of the computer is basically the same as the brain of a human being. It contains all the registers, control unit and the arithmetic logic unit (ALU). ALU considered as the most important subsystem in a digital computer. An arithmetic logic unit (ALU) is a digital circuit which performs arithmetic, logic and shift operations on two n-bit digital words. Functionally, an ALU can be divided up into three circuits: the arithmetic circuit, the logic circuit and the shift circuit. The 8-bit ALU was formed by combining four Full Adder and four Full Subtractor with five multiplexers as shown in the schematic diagram.

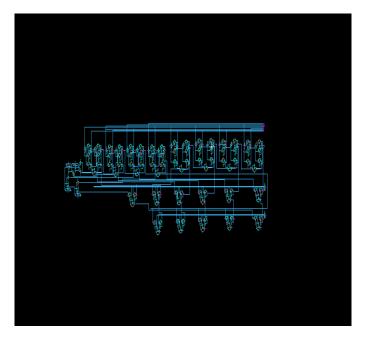

Fig. 14 Schematic diagram of ALU.

#### **SPICE Coding**

.Model NMOS NMOS kp=4.5u vto=1v gamma=0.4 lambda=0.02 phi=0.6v .Model PMOS PMOS kp=3.6u vto=-1v gamma=0.4 lambda=0.02 phi=0.6v Vdd Vdd Gnd 3.3v

Vin In Gnd Pulse(0 3.3v 0 1n 1n 10n 20n)

.tran 1n 100n

.dc VIn 0 3.3v .1v

.Power Vdd 1n 100n

.print V(In A) V(In B) V(In C) V(In D) V(In E) V(In F) V(In G) V(In H) V( select 0) V( select 1) V(Out A)

V(Out B) V(Out C) V(Out D) V(Out E)

\* SPICE export from S-Edit 12.50 Fri May 25 15:34:05 2012

Design: ALU Design1.sdb

\* Cell: Cell25

\* View: view0

\* Export as: Top-level Cell

\* Netlist port order: default

\* Exclude .model : no

\* Exclude .end: no

\* Expand paths: yes

\* Root path: C:\Users\haneef\Desktop\ALU\ALU Design1.sdb

\* Exclude global pins on subcircuits: no

\* Export control property name: SPICE

\* Wrap lines: no (to 0 characters)

MMOSFET\_P\_257 N\_326 N\_105 Vdd Vdd PMOS L=0.5u W=1.5u AD=1.8p PD=5.5u AS=1.8p PS=5.5u

MMOSFET\_N\_65 Gnd N\_54 N\_146 N\_152 NMOS L=0.5u W=0.5u AD=0.6p PD=3.5u AS=0.6p PS=3.5u

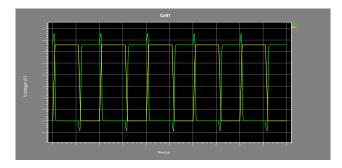

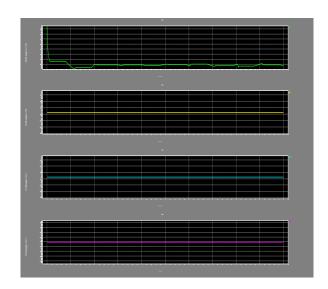

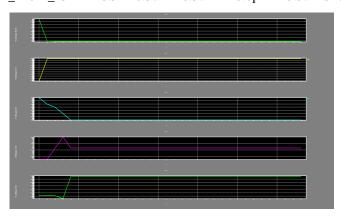

Fig. 15 DC analysis of ALU.

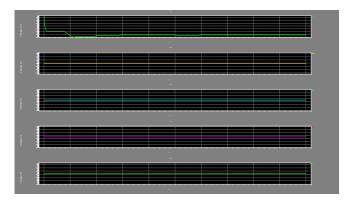

Fig. 16 AC analysis of ALU.

#### Conclusion

Tanner EDA Tools V12.5 with 0.5 sub-micron technology was used to develop the suggested ALU, and an analog design environment was used for simulation. The output waveforms' operational correctness was confirmed, and the voltage levels were examined. By employing the shorted-gate mode of the ALU in circuits that do not affect the delay, the suggested design can be further enhanced for better power usage. A multiply and accumulate (MAC) unit, which is widely used in signal processing, can be created by manipulating a modified multiplier and KSA. In reference [8], for designs larger than 32-bit. It can be used in place of a modified ALU after optimization. It is possible to conduct additional hardware analysis, such as layout simulation to examine the die area used for various components.

#### REFERENCES

- A design of low power 8-bit ALU ;Beom Seon Ryu; Jung Sok Yi; Kie Young Lee; Tae Won Cho TENCON 99. Proceedings of the IEEE Region 10 Conference 2018, Volume: 2 Digital ObjectIdentifier:

- [2] 10.1109/TENCON.1999.818556 ; Publication Year: 2016 ,

Page(s): 868 871 vol.2 ; IEEE Conference Publications .

- [3] Application Specific Low Power ALU Design ;Yu Zhou; Hui Guo Embedded and Ubiquitous Computing, 2008. EUC '08. IEEE/IFIP International Conference on Volume: 1 Digital Object Identifier: 10.1109/EUC.2008.81 Publication Year: 2008 , Page(s): 214 220 Cited by: 1; IEEE Conference Publications.

- [4] The power dissipation comparison of different ALU architectures; JunkaiSun; AnpingJiang Mechanical and Electrical Technology (ICMET), 2010 2nd International Conference on Digital Object Identifier: 10.1109 /ICMET.2010.5598395; Publication Year: 2010, Page(s): 430 433; IEEE Conference Publications.

- [5] Design of a high performance microcontroller; Hu Yue-li; Cao Jia-lin; Ran Feng; Liang Zhi-jian; High Density Microsystem Design and Packaging and Component Failure Analysis, 2004. HDP '04. Proceeding of the Sixth IEEE CPMT Conference on

- ;Digital Object Identifier: 10.1109/HPD.2004.1346667 ;Publication Year: 2004 , Page(s): 25 28 ; IEEE Conference Publications.

- [6] Design of a superconducting ALU with a 3-input XOR gate; Takahashi, K.; Nagasawa, S.; Hasegawa, H.; Miyahara, K.; Takai, H.; Enomoto, Y.; Applied Superconductivity, IEEE Transactions on Volume: 13, Issue:2, Part:1Digital Object Identifier: 10.1109/TASC.2003.813944 Publication Year: 2003, Page(s): 551 - 554 Cited by: 3; IEEE Journals & Magazines.

- [7] The 8051 Microcontroller and Embedded Systems; Second Edition;2007 Muhammad Ali Mazidi, Janice Gillispie Mazidi, Rolin D. McKinlay.

- [8] N. Shylashree, B.Venkatesh, M.T.Saurab, et.al, "Design and analysis of high-speed 8-bit ALU using 18 nm FinFET technology" Volume 25, pages 2349–2359, (2019).

- [9] H. V. R. Aradhya, M. T. Mahadikar, R. Muniraj, M. S. Suraj, M. Moiz and H. R. Madan, "Design, analysis and performance comparison of GNRFET based adiabatic 8-bit ALU," 2016 IEEE International Conference on Recent Trends in Electronics, Information & Communication Technology (RTEICT), Bangalore, India, 2016, pp. 1584-1588, doi: 10.1109/RTEICT.2016.7808099.

- [10] S. Anand and S. Indu, "A Low Power and High Speed 8-bit ALU Design using 17T Full Adder," 2020 7th International Conference on Signal Processing and Integrated Networks (SPIN), Noida, India, 2020, pp. 514-519, doi: 10.1109/SPIN48934.2020.9070844.

- [11] A. Sharma and R. Tiwari, "Low power 8-bit ALU design using full adder and multiplexer," 2016 International Conference on Wireless Communications, Signal Processing and Networking (WiSPNET), Chennai, India, 2016, pp. 2160-2164, doi: 10.1109/WiSPNET.2016.7566525.

- [12] L. Samal and C. Samal, "Designing a low power 8-bit application specific processor," 2014 International Conference on Green Computing Communication and Electrical Engineering (ICGCCEE), Coimbatore, India, 2014, pp. 1-5, doi: 10.1109/ICGCCEE.2014.6922238.

- [13] H. Singh, "Power Aware Design and Implementation of 8-bit Asynchronous Arithmetic and Logic Unit," 2009 IEEE International Advance Computing Conference, Patiala, India, 2009, pp. 1037-1047, doi: 10.1109/IADCC.2009.4809158.