#### **International Journal of**

## INTELLIGENT SYSTEMS AND APPLICATIONS IN **ENGINEERING**

ISSN:2147-6799 www.ijisae.org Original Research Paper

# Design and Performance Analysis of 8051 Microcontroller with 0.5 **Technology for Low Power Applications**

Vijay Singh, Vijay Kumar Ram, Yogesh Kumar, Rahul Prakash, Parul Varshney, Shikha Agarwal

**Submitted:** 25/10/2022 **Revised:** 14/12/2022 **Accepted:** 04/01/2023

Abstract: - In this paper, the innovative power getting is analyzed which minimizes the power dissipation in submicron circuits. The overall view this paper is to attain high speed, low power with alternative logic cells that lead to have reduced power dissipation. Here the total components are designed sub micro technology and observed that power analysis. This paper describes the implementation of a digital controller using an 8051 microcontroller and an active power line conditioning system to enhance the power quality in the distribution network. This study investigates the 8051 microcontroller's susceptibility to basic power analysis attacks. We have designed the Schematic and Layout of 8051 microcontroller, using tanner Tools (v12.5) and 0.5 submicron Technology. We have also done the transient Analysis and DC analysis of above-mentioned components using Tanner Tools (v12.5).

Keywords - 8051 Microcontroller, Modelsim (SE-4a), Tanner tools (V12.5), 6 -Transistor based RAM) and Xilinx (6.1i).

#### 1. Introduction

As we know that the 8051 microcontroller is the most

<sup>1</sup>Department of EIE, SCRIET, CCS University Meerut, Uttar Pradesh. scrietvijay2010@gmail.com <sup>2</sup>Department of ECE, SCRIET, CCS University Meerut, Uttar Pradesh. vijayk10ster@gmail.com <sup>3</sup>Department of ME, SCRIET, CCS University Meerut, Uttar Pradesh. yogeshyogi7916@gmail.com<sup>4</sup> Department of EIE SCRIET, CCS University Meerut, Uttar Pradesh. coolrahul2287@gmail.com 5Department of ECE, SCRIET, CCS University,

Meerut, Uttar Pradesh. parulspsvarshney@gmail.com

SCRIET, CCS University, Meerut, Uttar Pradesh.

<sup>6</sup>Department of AS

sagarwal.scriet@rediffmail.com

popular general-purpose microcontroller in use today. In this paper we have Analysis of 8051 microcontroller using CPU, RAM and interrupt controller before 8051 microcontroller design on VHDL Language in which check only waveform but we design on Tanner tools (v12.5) and VHDL both and analysis of DC and AC of 8051 microcontroller. We have drawn the schematic of all these three components using Tanner Tools from the schematic we study the Transient and DC analysis of the abovementioned components. Beside that we have also drawn tools and 0.5 sub-micron technology.

#### 2. Central Processing Unit OF 8051 Microcontrollers

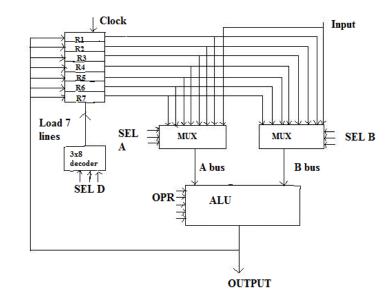

The Central Processing Unit (CPU) is the brain of the 8051 microcontroller that performs bulk of dataprocessing operations. In modern computational clusters these issues are usually prevented with the help of jobs and job schedulers, which postpone a job and schedule it later, when resources available [2]. Figure 1 shown the CPU architecture that we used drawing its schematic and layout using Tanner EDA tool V12.5.

Figure 1: Architecture of CPU

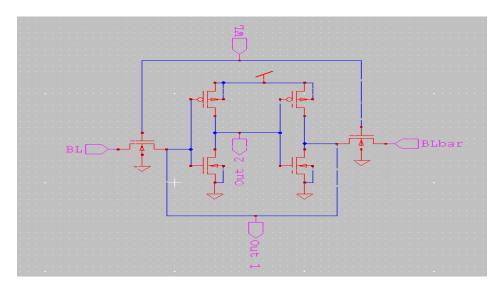

#### 3. 6-Transistors Based RAM

In this paper we have considered 6 Transistor based RAM. In this RAM out of Six Transistors are used as two inverters and the remaining two transistors are controlled by Word Line Figure (2) shows the circuit diagram of 6T Based RAM. A 128-byte internal asynchronous RAM and other synchronous peripherals including interrupts [3]. Using this, we have drawn schematic of using tanner tools. In addition to local RAM for storing intermediate results and specialized state machines to manage point

addition and doubling operations, they implemented field arithmetic operations in hardware. This method has a significant hardware cost even though it is very quick (no operand transfers occur during a point addition or doubling) [13-15]. Internal and external program memory access as well as external RAM memory access were tested separately. The correct operation of the timers, interrupt system, and serial port was then confirmed. Random program testing was then carried out to confirm that the core behaved correctly on test cases that would have gone unnoticed in earlier stages of verification [16].

Figure 2 Circuit diagram of RAM

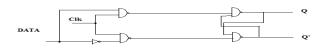

## 4. Interrupt Controller

Interrupt Controller is a component used to increase the speed of CPU. The Microcontroller includes the SPARC Processor an FPU, a memory controller, an Interrupt Controller and Peripheral devices in a single-chip [4,9-12]. **Figure 3** shown the circuit

diagram of interrupt controller using D- Flip - Flop. We have used this circuit diagram to design

schematic of Interrupt Controller using Tanner EDA Tool V12.5. **Figure 3** Circuit diagram Interrupt Controller.

Figure 3 Circuit diagram of D-Flip Flop.

## 5. Simulation and Results

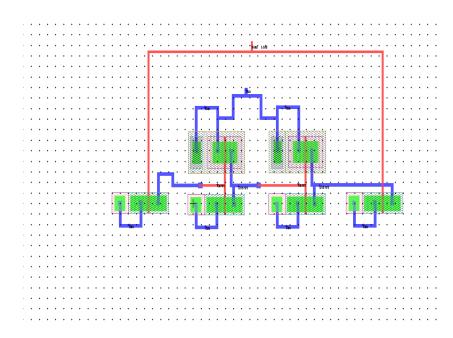

## 5.1 Layout of RAM

Using Tanner EDA Tool V12.5, we have designed the schematic and Layout of RAM. of RAM after doing simulation on Tanner Tool V12.5. **Figure 4**.

Figure.4 Layout of RAM

#### 5.1.1 Transient & DC analysis of RAM

We have done the Transient and DC analysis of RAM using tanner tool V12.5. **Figure 5** Shown the DC analysis of RAM.

Figure 5 DC Analysis of RAM

Figure 6 Transient Analysis of RAM

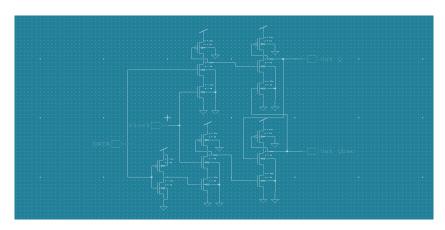

#### 5.2 **Schematic** Diagram of **Interrupt** Controller

Figure 7 shows the schematic diagram of interrupt controller designed using Tanner EDA Tool V12.5.

Figure 7 Schematic diagram of Interrupt controller

## 5.2.1 Transient & DC Analysis of Interrupt Controller

Figure 8 & Figure 9 shows the simulation results of Transient and DC analysis of Interrupt Controller using Tanner EDA Tool V12.5.

Figure 8 Transient Analysis of Interrupt Controller

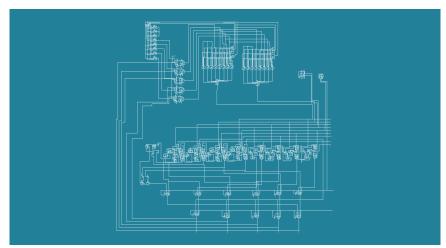

## 5.3 Schematic Diagram of CPU with **Interrupt Controller and RAM**

The control unit is used to lessen the Interrupt burden of the main CPU and to reduce the required CPU

performance, while message buffer RAM is used to store all messages transmitted and received[7].

Figure 9 shows the schematic diagram of CPU with Interrupt Controller And RAM. We have used Tanner Tools for designing this schematic diagram.

Figure 9 Schematic diagram of CPU with Interrupt Controller and RAM

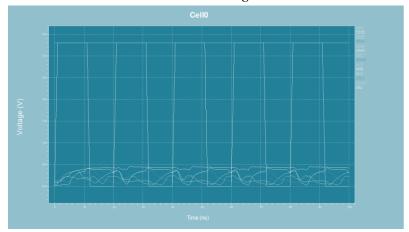

# **5.3.1** AC & DC Analysis of CPU with Interrupt Controller and RAM

Transient and DC analysis of CPU with Interrupt Controller and RAM is Shown in **Figure 10** & **Figure 11.**

Figure.10 Transient Analysis of CPU with Interrupt Controller and RAM

Figure.11 DC Analysis of CPU with Interrupt Controller and RAM

## 5.4 TIMING REPORT OF ALU

In CPU architecture, ALU of purely combinational ckt, independent multiplier and divider module, Ulticlocks architecture and hardwired control unit are adopted to get high speed [6,8].

We have generated the timing report of ALU after doing synthesis on Modelsim (SE-5.4a).

a) Clock Information: No clock signal found in this design.

- b) Timing Summary: Speed grade=6

- c) Minimum Period: No path found.

- d) Minimum input arrival time before clock: No path found.

- e) Maximum combinational path delay: 61.455 ns.

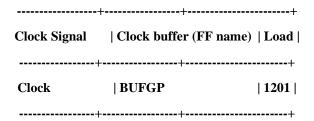

#### 5.5 TIMING REPORT OF RAM

The timing report of RAM is generated after doing synthesis on Modelsim.

#### **Generated After Place -And-Route**

#### **Clock Information**

## **Timing summary:**

Speed grade: 6

Minimum period: 13.859 ns (Maximum Frequency: 72.155MHz).

Minimum input arrival time before clock: 31.365 ns.

Maximum output required time after clock: 6.788 ns.

Maximum combinational path delay: No path found.

#### 6. Conclusion

We have designed the schematic and layout 8051 microcontroller using tanner tools and studied the transient and DC analysis of 6T based RAM. Interrupt controller of CPU of 8051 microcontroller from timing diagram generated using modelsim (SE-5.4a). Although our effort is focused on creating a new version of the simulator that operates at the machine-cycle or clock-cycle level, the current version operates at the instruction level. Performance will suffer as a result; however, two more enhancements will be made: i) Simulation of Timer 2 and new serial port modes for the 8052 microcontrollers; ii) Detailed simulation of the external bus. Additional enhancements could include the ability to undo and save/load states.

#### . References

- [1] M.Kovac,Asynchronous Microcontroller Simulation Model inVHDL,World Academyof Science, Engineering and Technology 452008, xkovac03@stud.feec.vutbr.cz, 2008.

- [2] Korotaev,K;"Hierarchical CPU Schedulers for Multiprocessor systems,Fair CPU scheduling and processes isolation", IEEE International on cluster computing,2005.

- [3] Chao Xue;Xiang cheng;Yang Guo;Yong Lian; "The design of a sub-nanojoule

- asynchronous 8051 Micro con troller with interface to external commercial memory",IEEE 8<sup>th</sup> International conference on ASICON 09,ASIC, 2009.

- [4] Kim,J.C; Lee,S.H.; Lee,D.Y.; Lee,J.H.;Jeong,W.C.;Park,H.J.;Mok,I.S.;"Si ngle-Chip implementation of a 32-bit Microcontroller for motor drive", Eleventh annual IEEE International onASIC conference 1998.

- [5] Ozawa,M.;Imai.M.;Ueno,Y.;Nakamura,H.;N anya,T.;"Performance evoluation of cascade ALU architecture for asynchronous superscale Processors" Seventh International symposium on asynchronous circuits and systems 2001.

- [6] Hu Yue-Li; Cao Jia-Lin; Ran Feng;Liang Zhi-Jian;"Design of a high performance microcontroller", Sixth IEEE CPMT conference on high density microsystem design and packaging and component failure analysis,2004.

- [7] Suk-Hyun Seo; Sang-Won Lee; Sung-Ho Hwang; Jae Wook Jeon; "Department of network Gateway between CAN and FlexRay Protocols for ECU Embedded Systems", International Joint conference on SICE-ICASE, 2006.

- [8] Alfredo del Río and Juan José Rodríguez Andina, "A SIMULATION TOOL FOR TEACHING/LEARNING THE 8051 MICROCONTROLLER" 0-7803-6424-4/00/\$10.00, 2000 IEEE.

- [9] [9]. V. Shvaichenko, D. Titkov and S. Kroshko, "The 8051-microcontroller application for complex signal Generating in model-based signal processing," 2009 10th International Conference The Experience of Designing and Application of CAD

- Systems in Microelectronics, Lviv, UKraine, 2009, pp. 260-260.

- [10] L. Ali, L. Rahman and S. Akhter, "Module-based Edukit for teaching and learning 8051 microcontrollers programming," 2017 IEEE International Conference on Telecommunications and Photonics (ICTP), Dhaka, Bangladesh, 2017, pp. 57-61, doi: 10.1109/ICTP.2017.8285918.

- [11] V. Kulkarni, P. P. Kulkarni and R. D. Kulkarni, "Design and Development of Software based Waveform Generation using Microcontroller 8051," 2019 International Conference on Nascent Technologies in Engineering (ICNTE), Navi Mumbai, India, 2019, pp. 1-7, doi: 10.1109/ICNTE44896.2019.8945834.

- [12] S. Arunaganesan, J. Adhavan, G. S. Reddy and M. Venkatesan, "Data acquisition system based on 8051 microcontroller for cutting tool temperature measurement," 2013 IEEE International Conference on Computational Intelligence and Computing Research, Enathi, India, 2013, pp. 1-4, doi: 10.1109/ ICCIC .2013.6724154.

- [13] Manuel Koschuch, Joachim Lechner, Andreas Weitzer, Johann Großsch"adl.

- Alexander ,Szekely, Stefan Tillich, and Johannes Wolkerstorfer "Hardware/Software Co-design of Elliptic Curve Cryptography on an 8051 Microcontroller", CHES 2006, LNCS 4249, pp. 430–444, 2006, International Association for Cryptologic Research 2006.

- [14] Shi Yuanyuan, Liu Jia and Liu Runsheng, "Single-chip speech recognition system based on 8051 Micro controller core," in IEEE Transactions on Consumer Electronics, vol. 47, no. 1, pp. 149-153, Feb. 2001,doi: 10.1109/30.920433.

- [15] K. Y. Leung, K. Leung and D. R. Holberg, "A Dual Low Power 1/2 LSB NL 16b/1Msample/s SAR A/D Converter with on-chip Microcontroller," 2006 IEEE Asian Solid-State Circuits Conference, Hangzhou, China, 2006, pp. 51-54, doi: 10.1109/ASSCC.2006.357849.

- [16] A. J. Salim, M. Othman and M. A. M. Ali, "Integration of 8051 With DSP in Xilinx FPGA," 2006 IEEE International Conference on Semiconductor Electronics, Kuala Lumpur, Malaysia, 2006, pp. 562-566, doi: 10.1109/SMELEC.2006.380694.