Design of High-Performance GDI Logic based 8-Tap FIR Filter at 45nm CMOS Technology using Nikhilam Multiplier

Keywords:

GDI technique, FIR filter design, MAC, Multiplier, Full adderAbstract

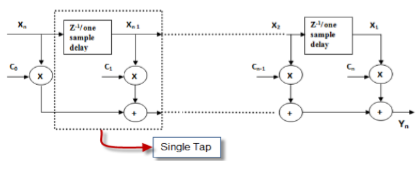

Over the past few decades, advances in IC technology have steadily shrunk feature sizes, necessitating the placement of more operational circuits on every chip. In designing digital circuits, a novel GDI based circuit is indeed the center of consideration, since it requires less power and achieves greater efficiency. GDI-based circuits mimic CMOS transistors but feature fewer transistors with a greater capacity for performance and reliability. This paper investigates the modelling and implementation of a Finite Impulse-Response (FIR) block developed utilizing GDI-based circuits as well as basic blocks. In this study, an eight-tap FIR architecture relying on GDI cells is created. The results reveal that even a FIR architecture with eight taps and GDI delivers reduced power consumption and performance improvement.

Downloads

References

N. S. Rai, P. S. B. S, M. Y. P, A. P. Chavan, and H. V. R. Aradhya, “Design and implementation of 16 tap FIR filter for DSP Applications,” 2018 Second International Conference on Advances in Electronics, Computers and Communications (ICAECC) (2018).

R. A. S. Durai singh, A. J. Deva, J. P. Jeganatha, M. A. B. Saleem, and Tharmavel Abirami, “Modelling and Analysis of Modified Baugh-Wooley Multiplier Using Gate Diffusion Input and Improved Shannon Adder,” International Journal of Pure and Applied Mathematics, vol. 118, no. 22, pp. 773-777, 2018.

Alaria, S. K., A. . Raj, V. Sharma, and V. Kumar. “Simulation and Analysis of Hand Gesture Recognition for Indian Sign Language Using CNN”. International Journal on Recent and Innovation Trends in Computing and Communication, vol. 10, no. 4, Apr. 2022, pp. 10-14, doi:10.17762/ijritcc.v10i4.5556.

B. K. Mohanty, and P. K. Meher, “A High-Performance FIR Filter Architecture for Fixed and Reconfigurable Applications”, IEEE Transactions on Very Large-Scale Integration (VLSI) Systems, vol. 24, no. 2, pp. 444–452, 2016.

Mohan Shoba, and Rangaswamy Nakkeeran, “GDI based full adders for energy efficient arithmetic applications,” Engineering Science and Technology, an International Journal, vol. 19, no. 1, pp. 485–496, 2016.

A. Morgenshtein, A. Fish, and I.A. Wagner, “Gate-Diffusion Input (GDI)- Annual power efficient method for digital circuits,” Proc. 14th Annual IEEE Int. ASIC/SOC Conf., 2001, pp. 39-43.

A. Morgenshtein, A. Fish, and I. A. Wagner, “Gate-Diffusion Input (GDI): A Power Efficient Method for Digital Combinatorial Circuits,” IEEE Transactions on Very LargeScale Integration (VLSI) Systems, vol. 10, no. 5, 2002.

H. T. Bui, Y. Wang, and Y. Jiang, “Design and analysis of lowpower 10-transistor full adders using novel XOR-XNOR gates,”, IEEE Trans. Circuits Syst. II, Analog Digit. Signal Process, vol. 49, no. 1, pp. 25–30, Jan 2002.

M. Vesterbacka, “A 14-transistor CMOS full adder with full voltage swing nodes,” in Proc. IEEE Workshop Signal Processing Systems, pp. 713–722, Oct 1999.

A. P. Chandrakasan, and R. W. Brodersen, “Low Power Digital CMOS Design,” Norwell, MA: Kluwer, 1995.

K. Yano, et al., “A 3.8 ns CMOS 16x16 multiplier using complimentary pass-transistor logic,” IEEE J. Solid-State Circuits, vol. 25, no. 2, pp. 388–395, Apr 1990.

Ghazaly, N. M. . (2022). Data Catalogue Approaches, Implementation and Adoption: A Study of Purpose of Data Catalogue. International Journal on Future Revolution in Computer Science &Amp; Communication Engineering, 8(1), 01–04. https://doi.org/10.17762/ijfrcsce.v8i1.2063

Chip-Hong Chang, Jiangmin Gu, and Mingyan Zhang, “A Review of 0.18-_m Full Adder Performances for Tree Structured Arithmetic Circuits,” IEEE Trans. On Very LargeScale Integration (VLSI) Systems, vol. 13, no. 6, pp. 686–695, June 2005.

N. Zhuang, and H. Hu, “A new design of the CMOS full adder,” IEEE J. Solid-State Circuits, vol. 27, no. 5, pp. 840–844, May 1992.

C. Chang, J. Gu, and M. Zhang, “Ultra Low-Voltage Low- Power CMOS 4-2 and 5-2 Compressors for Fast Arithmetic Circuits,” IEEE Transactions on Circuits & Systems, vol. 51, no. 10, pp. 1985-1997, Oct. 2004. Jan

M. Rabaey, A. Chandrakasan, and B. Nikolic, “Digital Integrated Circuit. Prentice Hall Publications: Inadi, 2006,” vol. 11, pp. 590

F. Moradi Dag, T. Wisland, H. Mahmoodi, S. Aunet, T. Vucao, and A. Peiravi, “Ultra Low Power Full Adder Topologies,” San Francisco State Univ.2009 IEEE, pp. 3160.

R. Zimmermann, and W. Fichtner, “Low-power logic styles: CMOS versus pass-transistor logic,” IEEE J. Solid-State Circuits, vol. 32, no. 7, pp. 1079–1090, Jul 1997

Andrie Dazlee, N. M. A., Abdul Khalil, S., Abdul-Rahman, S., & Mutalib, S. (2022). Object Detection for Autonomous Vehicles with Sensor-based Technology Using YOLO. International Journal of Intelligent Systems and Applications in Engineering, 10(1), 129–134. https://doi.org/10.18201/ijisae.2022.276

N. H. E. Weste, and D. M. Harris, “CMOS VLSI Design: A Circuits and Systems Perspective,” 4th ed. Boston, MA, USA: Addison-Wesley, 2010.

A. M. Shams, T. K. Darwish, and M. A. Bayoumi, “Performance analysis of low-power 1-bit CMOS full adder cells,” IEEE Trans. Very Large Scale Integr. (VLSI) Syst, vol. 10, no. 1, pp. 20–29, Feb 2002.

M. Alioto, G. Di Cataldo, and G. Palumbo, “Mixed full adder topologies for high-performance low-power arithmetic circuits,” Microelectron. J., vol. 38, no. 1, pp. 130–139, Jan 2007.

C. K. Tung, Y. C. Hung, S. H. Shieh, and G. S. Huang, “A low-power high-speed hybrid CMOS full adder for embedded system,” in Proc. IEEE Conf. Design Diagnostics Electron. Circuits Syst, vol. 13, pp. 1–4, Apr. 2007.

Ahmed Cherif Megri, Sameer Hamoush, Ismail Zayd Megri, Yao Yu. (2021). Advanced Manufacturing Online STEM Education Pipeline for Early-College and High School Students. Journal of Online Engineering Education, 12(2), 01–06. Retrieved from http://onlineengineeringeducation.com/index.php/joee/article/view/47

M. Aguirre-Hernandez, and M. Linares-Aranda, “CMOS full-adders for energy-efficient arithmetic applications,” IEEE Trans. Very Large Scale Integr. (VLSI) Syst, vol. 19, no. 4, pp. 718–721, Apr 2011.

S. Goel, A. Kumar, and M. A. Bayoumi, “Design of robust, energyefficient full adders for deep-submicrometer design using hybrid-CMOS logic style,” IEEE Trans. Very Large Scale Integr. (VLSI) Syst, vol. 14, no. 12, pp. 1309–1321, Dec 2006.

I. Hassoune, D. Flandre, I. O'Connor, and J. Legat, "ULPFA: A New Efficient Design of a Power-Aware Full Adder," in IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 57, no. 8, pp. 2066- 2074, Aug 2010.

R. F. Mirzaee, M. H. Moaiyeri, H. Khorsand, and K. Navi, “A New Robust and Hybrid High-Performance Full Adder Cell,” Journal of Circuits, Systems and Computers, vol. 20, no. 4, pp. 641-655, 2011.

M. C. Parameshwara, and H. C. Srinivasaiah, “Low-Power Hybrid 1-Bit Full Adder Circuit for Energy Efficient Arithmetic Applications,” Journal of Circuits, Systems and Computers, vol. 26, no. 1, pp. 1-15, 2017.

P. Kumar, and R. K. Sharma, “An Energy Efficient Logic Approch to Implement CMOS Full Adder,” Journal of Circuits, Systems and Computers, vol. 26, no. 5, pp. 1-20, 2017.

M. Shoba, and R. Nakkeeran, “GDI based full adders for energy efficient arithmetic applications,” Engineering Science and Technology, an International Journal, vol. 19, no. 1, pp. 485-496, 2016.

Mehedi Hasan, M. D. Jobayer Hossein, Mainul Hossain, Hasan U. Zaman, Senior Member, IEEE and Sharnali Islam, “Design of a Scalable Low-Power 1-bit Hybrid Full Adder for Fast Computation”, IEEE Transactions on Circuits and Systems II: Express Briefs, vol. 1, 2019.

C. S. Wallace, “A suggestion for a fast multiplier,” IEEE Trans. Elect. Comput. vol. 13, no. 1, pp. 14–17, 1964.

R. S. Waters, and E. E. Swartzlander, “A reduced complexity wallace multiplier reduction,” IEEE Trans. Comput, vol. 59, no. 8, pp. 1134–1137, 2010.

S. Asif, and Y. Kong, “Analysis of different architectures of counter based wallace multipliers,” In Proceedings of the 2015 Tenth International Conference on Computer Engineering Systems (ICCES), pp. 139–144, 2015.

S. Asif, and Y. Kong, “Design of an algorithmic wallace multiplier using high speed counters,” In Proceedings of the 2015 Tenth International Conference on Computer Engineering Systems (ICCES), pp. 133–138, 2015. https://doi.org/10.1109/ICCES.2015.7393033

C. Fritz, and A. T. Fam. “Fast binary counters based on symmetric stacking,” IEEE Trans. Very Large Scale Integ. (VLSI) Syst, vol. 25, no. 10, pp. 2971–2975, 2017. https://doi.org/10.1109/TVLSI.2017.2723475

M. Madheswaran, and D. Malathi, “Design of Low Power FIR Filter Using 6T Full Adder”, Australian Journal of Basic and Applied Sciences, vol. 8, no. 18, pp. 72-78, December 2014.

B. S. Pasuluri, and V. J. K Kishor Sonti, “Performance Analysis of 8-Bit Vedic Multipliers Using HDL Programming. In: Kumar A., Paprzycki M., Gunjan V. (eds) ICDSMLA 2019. Lecture Notes in Electrical Engineering, Springer, Singapore, vol. 601, 2020. https://doi.org/10.1007/978-981-15-1420-3_114

Binduswetha, Pasuluri, and V. J. K. Kishor Sonti, “Design of Vedic multiplier-based FIR filter for signal processing applications," Journal of Physics: conference series IOP publishing Ltd.1921, pp. 012047, 2021. doi: 10.1088/1742-6596/1921/1/012047. impact factor: 1.1., ISSN 1742588, 17426596. https://iopscience.iop.org/article/10.1088/1742-6596/1921/1/012047

Binduswetha, and Pasuluri, V. J. K. Kishor Sonti, “Design and Analysis of Instrumentation amplifier using 45nm technology”, in Informatica Journal, vol. 32, no. 11, ISSN:0868-4952, pp. 37-48. IF: 1.928,2021.

B. S. Pasuluri, and V. J. K. K. Sonti, "Design and Performance Analysis of Analog Filter and Digital Filter with Vedic Multipliers in Bio-Medical Applications," 2022 International Conference for Advancement in Technology (ICONAT), pp. 1-82022, doi: 10.1109/ICONAT53423.2022.9725831.https://ieeexplore.ieee.org/document/9725831

Binduswetha Pasuluri, and V. J. K. Kishor Sonti, 1570780638 “Reducing computational complexity in digital circuit designing using Ancient Mathematics” in IEEE Delhi Section Conference DELCON 2022, IEEE, pp..978-1-6654-5883-2/22. https://ieeexplore.ieee.org/document/9753237/

Binduswetha Pasuluri, and V. J. K. Kishor Sonti, “FPGA implementation of enhanced throughput design of AES architecture using nikhilam sutra”, in Tianjin Daxue Xuebao (Ziran Kexue yu Gongcheng Jishu Ban)/Journal of Tianjin University Science and Technology, vol. 55, ISSN.0493-2137, June 2022. https://tianjindaxuexuebao.com/details.php?id=DOI:10.17605/OSF.IO/5MEJW

Downloads

Published

How to Cite

Issue

Section

License

This work is licensed under a Creative Commons Attribution-ShareAlike 4.0 International License.

All papers should be submitted electronically. All submitted manuscripts must be original work that is not under submission at another journal or under consideration for publication in another form, such as a monograph or chapter of a book. Authors of submitted papers are obligated not to submit their paper for publication elsewhere until an editorial decision is rendered on their submission. Further, authors of accepted papers are prohibited from publishing the results in other publications that appear before the paper is published in the Journal unless they receive approval for doing so from the Editor-In-Chief.

IJISAE open access articles are licensed under a Creative Commons Attribution-ShareAlike 4.0 International License. This license lets the audience to give appropriate credit, provide a link to the license, and indicate if changes were made and if they remix, transform, or build upon the material, they must distribute contributions under the same license as the original.