Design an Efficient Braun Multiplier Using KSA Based CMOS Logics

Keywords:

Parallel Prefix Adder, Braun Multiplier, Complementary Inverter logic, Kogge Stone Adder, Pass Transistor LogicAbstract

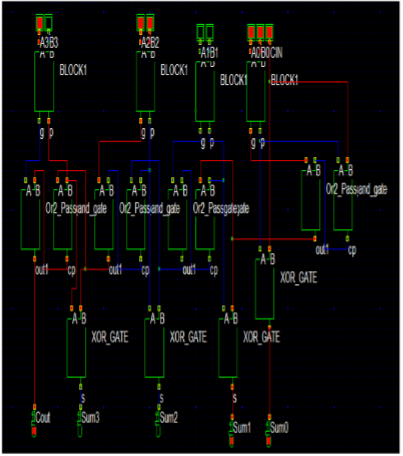

The addition is the basic process of digital electronics in DSP and VLSI processing applications. In earlier days, many researchers have developed various binary adders and technologies have used to precede the addition process in digital electronic applications. Half and Full Adders are the two fundamental binary adders with limited to the addition up to 3 bits. If the addition required more than 4 bits, then the basic HA and FA adders has not suitable. In that situation, the binary addition process has done with the help of high grade binary carry adders such as RCA, CSA, CSLA, CLA. Due the carry delay problem, the Parallel Prefix Adder (PPA) has selected as the high speed adder to do the binary addition with less delay by researched developers. Generally, the addition is used to implement the binary multiplication process in digital electronics. This paper has proposed the design of Braun Array Multiplier (BAM) using Kogge Stone Parallel Prefix Adder based CMOS logics. Belongs to that, this work has proposed the KSA based Pass Transistor logic, NMOS with Complementary Inverter logic and PMOS with Complementary Inverter logic. All the logics have applied in the Braun Array Multiplier to enhance the performance of multiplication process. The proposed logics have compared with the aspects like area, power and layout size. Microwind tool is able to generate the simulation and analysis results.

Downloads

References

N. Poornima, V. S. Kancahana Bhsaskaran, “Area Efficient Hybrid Parallel Prefix Adders,” in Procedia Materials Science, Vol.10, 2015, pp. 371-380.

S. Daphni, K. S. Vijula Grace, “Design and Analysis of 32-bit Parallel Prefix Adders for Low Power VLSI Applications,” in Advances in Science, Technology and Engineering Systems Journal Vol. 4, No. 2, 2019, pp. 102-106.

Paithane, P. M., & Kakarwal, D. (2022). Automatic Pancreas Segmentation using A Novel Modified Semantic Deep Learning Bottom-Up Approach. International Journal of Intelligent Systems and Applications in Engineering, 10(1), 98–104. https://doi.org/10.18201/ijisae.2022.272

S. Daphni, K. S. Vijula Grace, “A review analysis of Parallel Prefix Adders for better performnce in VLSI applications,” in Proceedings of IEEE International Conference on Circuits and Systems, 2017, pp.103-106.

Alaria, S. K., A. . Raj, V. Sharma, and V. Kumar. “Simulation and Analysis of Hand Gesture Recognition for Indian Sign Language Using CNN”. International Journal on Recent and Innovation Trends in Computing and Communication, vol. 10, no. 4, Apr. 2022, pp. 10-14, doi:10.17762/ijritcc.v10i4.5556.

S. Rakesh, K. S. Vijula Grace, “A comprehensive review on the VLSI design performance of different Parallel Prefix Adders,” in Materials today proceedings, Vol.11, No. 3, 2019, pp. 1001-1009.

Reshma Mary James, Ajith Ravindran, “Review of Full Adder Performance Analysis Using Kogge Stone Adder And Magnetic Tunnel Junction,” in Fourth International Conference on Devices, Circuits and Systems (ICDCS'18), 2018, pp. 84-90.

S. Daphni, K. S. Vijula Grace, “A review analysis of Parallel Prefix Adders for better performance in VLSI Applications,” in Proceedings of 2017 IEEE International Conference on Circuits and Systems, 2018, pp. 103-106.

Chaudhary, D. S. . (2022). Analysis of Concept of Big Data Process, Strategies, Adoption and Implementation. International Journal on Future Revolution in Computer Science &Amp; Communication Engineering, 8(1), 05–08. https://doi.org/10.17762/ijfrcsce.v8i1.2065

Anjana. R, Abishna. B, Harshitha. M.S, Abhishek. E, Ravichandra.V, Dr. Suma M.S, “Implementation of Vedic Multiplier using Kogge-Stone Adder,” International Conference on Embedded Systems - (ICES), 2014, 28-31.

S. Daphni, K. S. Vijula Grace, “A review analysis of Reverse Converter based on RNS in Signal Processing,” in International Journal of Scientific and Technology Research, Vol. 9, No. 2, 2020, pp. 1686-1689.

S. Daphni, K. S. Vijula Grace, “Design and Anaylsis of 32-bit Reverse Converter based on low power Parallel Prefix Adder,” in International Journal of Engineering and Advance Technology, Vol. 9, No. 1, 2019, pp. 3028-3031

J. Jabłoński, R. Dylewski, “The optimization of parallel multiplication,” in IFAC Proceedings Volumes, Vol.46, No.28, 2013, pp. 187-191.

André Sanches Fonseca Sobrinho. (2020). An Embedded Systems Remote Course. Journal of Online Engineering Education, 11(2), 01–07. Retrieved from http://onlineengineeringeducation.com/index.php/joee/article/view/39

J. Jabłoński, R. Dylewski, “The optimization of parallel multiplication,” in IFAC Proceedings Volumes, Vol.46, No.28, 2013, pp. 187-191.

S. Daphni, K. S. Vijula Grace, “Design an Area Efficient Kogge Stone Adder using Pass Transistor Logic,” in Proceedings of the 3rd International Conference on Intelligent Communication Technologies and Virtual Mobile Networks, ICICV, 2021, pp. 614–618.

Deeksha Kiran D K, Shilpa R and Kavyashree B, “VLSI Implementation of Braun Multiplier using Full adder,” in International Conference on Current Trends in Computer, Electrical, Electronics and Communication (ICCTCEEC), 2017, pp. 499-504.

Christian Martyn Jones, Satnam Singh Dlay and Raouf Gorgui Naguib, “Berger Check Prediction for Concurrent Error Detection in The Braun Array Multiplier,” in ICECS, 1996, pp. 81-84.

Seungbum Baek, Jason K. Eshraghian, Sang-Hyun Ahn, Alex James, Kyoungrok Cho, “A Memristor-CMOS Braun Multiplier Array for Arithmetic Pipelining,” in IEEE, 2019, pp. 735-738.

Downloads

Published

How to Cite

Issue

Section

License

This work is licensed under a Creative Commons Attribution-ShareAlike 4.0 International License.

All papers should be submitted electronically. All submitted manuscripts must be original work that is not under submission at another journal or under consideration for publication in another form, such as a monograph or chapter of a book. Authors of submitted papers are obligated not to submit their paper for publication elsewhere until an editorial decision is rendered on their submission. Further, authors of accepted papers are prohibited from publishing the results in other publications that appear before the paper is published in the Journal unless they receive approval for doing so from the Editor-In-Chief.

IJISAE open access articles are licensed under a Creative Commons Attribution-ShareAlike 4.0 International License. This license lets the audience to give appropriate credit, provide a link to the license, and indicate if changes were made and if they remix, transform, or build upon the material, they must distribute contributions under the same license as the original.