A Leakage Reduction Charge Pump based Domino Logic for Low Power VLSI Circuits

Keywords:

Charge pump, domino logic, leakage reduction, Low power VLSIAbstract

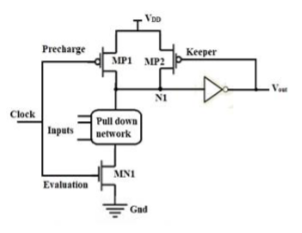

A new leakage reduction domino logic circuit with a charge pump and a transistor is proposed to improve the performance of the high fan-in circuits. The charge pump and two parallel connected transistors are used to improve the signal strength of the output and reducing the delay. Keeper transistor is used to restore the logic levels of the node. An additional transistor is used to reduce the leakage currents and reducing the power dissipation. The proposed circuit is also applied for domino OR logic function. The proposed technique has a lesser delay and power dissipation compared to the standard domino logic. The proposed technique is more suitable for high speed and low power domino OR logic and can be implemented to the high fan-in gates.

Downloads

References

J. M. Rabaey, A. Chandrakasan and B. Nikolic, “Digital Integrated circuits: A design perspective, “Second Edition. Prentice-Hall of India, India, 2016.

A. Karthikeyan and P.S. Mallick, “Body-biased subthreshold bootstrapped CMOS driver, “Journal of Circuits, Systems, and Computers, vol. 28, no. 3, pp. 1950051-1- 1950051-16, 2019.

V. Kursun and E. G. Friedman, “Domino logic with dynamic body biased keeper, “in Proc. of the 28th European Solid-State Circuits Conference, Florence, Italy, pp. 675-678, 2002.

V. Kursun and E. G. Friedman, “Domino logic with variable threshold voltage keeper, “IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol.11, no. 6, India, 2003, pp. 1080-1093.

G. Na et al, “Robustness aware high performance high fan-in domino OR logic design, “Journal of Semiconductors, vol. 30, no. 6, pp. 065005-1-065005-4, 2009.

H. Mahmoodi-Meimand and K. Roy, “Diode-footed domino: a leakage-tolerant high fan-in dynamic circuit design style, “IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 51, no. 3, pp. 495-503, 2004.

V. Kursun and E. G. Friedman, “Sleep switch dual threshold voltage domino logic with reduced standby leakage current, “IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 12, no. 5, pp. 485-496, 2004.

Z. Liu and V. Kursun, “PMOS-only sleep switch dual-threshold voltage domino logic in sub-65-nm CMOS technologies, “IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 15, no. 12, pp. 1311-1319, 2007.

N. Gong. et al, “Analysis and optimization of leakage current characteristics in sub- 65nm dual Vt footed domino circuits, “Microelectronics Journal, vol. 39, no. 9, pp. 1149-1155, 2008.

J. H. Wang, et al, “Monte carlo analysis of a low power domino gate under parameter fluctuation, “Journal of Semiconductors, vol. 30, no. 12, pp. 125010-1-125010-5, 2009.

V. Mahor and M. Pattanaik, “A state-of-the-art current mirror-based reliable wide fan-in FinFET domino OR gate design, “Circuits, Systems and Signal Processing, vol. 37, pp. 475-499, 2018.

A. K. Dadoria, et al, “Ultra-low power FinFET-based domino circuits, “International Journal of Electronics, vol. 104, no. 6, pp. 952–967, 2017.

S. Garg and T. K. Gupta, “A new technique for designing low-power high-speed domino logic circuits in FinFET technology, “Journal of Circuits, Systems, and Computers, vol. 28, no. 10, pp. 1950165 (1-22), 2019.

A. K. Dadoria, et al, “Performance evaluation of domino logic circuits for wide fan-in gates with FinFET, “Microsystem Technologies, vol. 34, pp. 3341-3348, 2018.

F. Moradi, et al, “Domino logic designs for high-performance and leakage-tolerant applications, “Integration, the VLSI Journal, vol. 46, no. 3, pp. 247– 254, 2013.

F. Moradi, et al, “A new leakage-tolerant design for high fan-in domino circuits, in Proc. of the 16th International conference on microelectronics, ICM, Tunisian, 2004.

T. K. Gupta and K. Khare, “Lector with footed-diode inverter: A technique for leakage reduction in domino circuits, “Circuits, Systems, and Signal Processing, vol. 32, pp. 2707-2722, 2013.

M. Asyaei and F. Moradi, “A domino circuit technique for noise-immune high fan-in gates, “Journal of Circuits, Systems, and Computers, vol. 27, no. 10, pp. 1850151 (1-23), 2018.

A. Kumar and R. K. Nagaria, “A new leakage-tolerant high speed comparator based domino gate for wide fan-in OR logic for low power VLSI circuits, “Integration, the VLSI Journal, vol. 63, pp. 174– 181, 2018.

A. K. Pandey, et al, “Analysis of noise immunity for wide OR footless domino circuit using keeper controlling network, “Circuits, Systems and Signal Processing, vol. 37, pp. 4599-4616, 2018.

A. A. Angeline and V. S Kanchana Bhaaskaran, “High speed wide fan-in designs using clock controlled dual keeper domino logic circuits, “ETRI Journal, vol. 41, no. 3, pp. 383-395, 2019.

A. A. Angeline and V. S Kanchana Bhaaskaran, “Design impacts of delay invariant high-speed clock delayed dual keeper domino circuit, “IET Circuits, Devices & Systems, vol. 13, no. 8, pp. 1134-1141, 2019.

J. Muralidharan and P. Manimegalai, “Current comparison domino based CHSK domino logic technique for rapid progression and low power alleviation, “International Journal of Electrical and Computer Engineering, vol. 7, no. 5, pp. 2468-2473, 2017.

Gupta, D. J. . (2022). A Study on Various Cloud Computing Technologies, Implementation Process, Categories and Application Use in Organisation. International Journal on Future Revolution in Computer Science &Amp; Communication Engineering, 8(1), 09–12. https://doi.org/10.17762/ijfrcsce.v8i1.2064

Jang Bahadur, D. K. ., and L. . Lakshmanan. “Virtual Infrastructure Based Routing Algorithm for IoT Enabled Wireless Sensor Networks With Mobile Gateway”. International Journal on Recent and Innovation Trends in Computing and Communication, vol. 10, no. 8, Aug. 2022, pp. 96-103, doi:10.17762/ijritcc.v10i8.5681.

S. Garg and T. K. Gupta, “Low leakage domino logic circuit for wide fan-in gates using CNTFET, “IET Circuits, Devices & Systems, vol. 13, no. 2, pp. 163-173, 2019

S. Garg, et al, “A 4:1 multiplexer using dual chirality CNTFET based domino logic in nano-scale technology, “International Journal of Electronics, vol. 107, no. 4, pp. 513-541, 2019.

M. J. Traum, J. Fiorentine. (2021). Rapid Evaluation On-Line Assessment of Student Learning Gains for Just-In-Time Course Modification. Journal of Online Engineering Education, 12(1), 06–13. Retrieved from http://onlineengineeringeducation.com/index.php/joee/article/view/45

S. Singhal, et al, “Power reduction in domino logic using clock gating in 16nm CMOS technology, in Proc. of the 6th International Conference on Signal Processing and Integrated Networks (SPIN), Noida, India, 2019, pp. 274-277.

Chawla, A. (2022). Phishing website analysis and detection using Machine Learning. International Journal of Intelligent Systems and Applications in Engineering, 10(1), 10–16. https://doi.org/10.18201/ijisae.2022.262

Downloads

Published

How to Cite

Issue

Section

License

This work is licensed under a Creative Commons Attribution-ShareAlike 4.0 International License.

All papers should be submitted electronically. All submitted manuscripts must be original work that is not under submission at another journal or under consideration for publication in another form, such as a monograph or chapter of a book. Authors of submitted papers are obligated not to submit their paper for publication elsewhere until an editorial decision is rendered on their submission. Further, authors of accepted papers are prohibited from publishing the results in other publications that appear before the paper is published in the Journal unless they receive approval for doing so from the Editor-In-Chief.

IJISAE open access articles are licensed under a Creative Commons Attribution-ShareAlike 4.0 International License. This license lets the audience to give appropriate credit, provide a link to the license, and indicate if changes were made and if they remix, transform, or build upon the material, they must distribute contributions under the same license as the original.