Analogy of Distinct Constructions of FinFET GDI Full Adder

Keywords:

CMOS, Fin-Field Effect Transistor, Full Adder, Gate-Diffusion input, Performance analysis, PowerAbstract

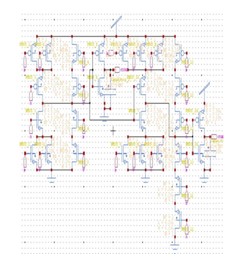

In this work a diversification of adding methods including the engrossing of the proposed Fin-Field Effect Transistor technology, are analyzed. A variety of different Complementary Metal Oxide Semiconductor Full Adder reconstruction approaches have been analyzed for area, run time, potential and figure of merit. Study of facts has been examined for conventional circuits. Hypothetically sophisticated Fin-Field Effect Transistor Gate Diffusion Input adder, designed framework principles antiquated outstandingly improved the structure of full adder in contrast with the conventional methods. In this technique the Fin-Field Effect Transistor technology achieves 90%reduction of chip area, power is abated by 73% and run time is reduced compared to the referred full adder circuits. Synthesis results of proposed adder have been employed with the help of cadence Electronic Design Automation tool. The Proposed Fin-Field Effect Transistor Gate Diffusion Input adder leads to high performance, low path delay and reduce lack of synchronization

Downloads

References

Ch.RajeshBabu, T Venkatesh, E Jagadeeshwara Rao “Conventional Full Adder Fin-Field Effect Transistor Implementation using Transmission”, International Journal of Advanced Trends in Computer Science and Engineering, Volume 7, No.6, November-2018.

RichaSaraswatl, ,Shyam Akashe2,” Designing and Simulation of Full Adder Cell Using Fin-Field Effect Transistor Technique”, International Conference on Intelligent System and Control,2013.

SaradinduPandal, ABanerjee,et.al, "Power and Delay Comparison in between Different types of Full Adder Circuits", International Journal of Advanced Research in Electrical, Electronics and Instrumentation Engineering Vol. I, Issue 3, September 2012, pp 168-172.

Walid Ibrahim, Azam Beg, and ValeriuBeiu, "Highly Reliable and Low-Power Full Adder Cell", 2011 11th IEEE International Conference on Nanotechnology Portland Marriott August, 2011.

Mariano Aguirre-Hernandez and Monico Linares-Aranda, "CMOS Full Adders for Energy-Efficient Arithmetic Applications", IEEE Transactions On Very Large Scale Integration (Vlsi) Systems, Vol. 19, No. 4, April 2011.

N. M. Chore, and R N. Mandavgane, "A Survey of Low Power High Speed I Bit Full Adder", Proceeding of the 12th International Conference on Networking, VLSI and Signal Processing, pp. 302-307, 2010.

Dan Wang, Maofeng Yang, Wu Cheng, Xuguang Guan, Zhangming Zhu, Yintang Yang, "Novel Low Power Full Adder Cells in 180nm CMOS Technology", 4th IEEE Conference on Industrial Electronics and Applications, ICIEA 2009, pp 430-433.

KeivanNavi and Omid Kavehei, "Low-Power and High-Performance 1- Bit CMOS Full-Adder Cell", JOURNAL OF COMPUTERS, VOL. 3, NO.2, FEBRUARY 2008, pp48-54.

VahidMoalemi and Ali Afzali-Kusha, “Subthreshold 1-bit Full adder cells in sub-100nm technologies”, IEEE Computer Society Annual Symposium on VLSI (ISVLSI-07), Porto Alegre, Brazil, March, 2007.

S. Goel, A. Kumar, and M. A. Bayoumi, “Design of robust, energy- efficient full adders for deep-submicrometer design using hybrid-CMOS logic style,” IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol. 14, no. 12, pp. 1309–1321, Dec. 2006.

S. Goel, A. Kumar, and M. A. Bayoumi, “Design of robust, energy- efficient full adders for deep-submicrometer design using hybrid-CMOS logic style,” IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol. 14, no. 12, pp. 1309–1321, Dec. 2006.

K. Kim, K. K. Das, R V. Joshi, and c.-T. Chuang, "Leakage power analysis of 25-nm double-gate CMOS devices and circuits," IEEE Trans. Electron Devices, vol. 52, no. 5, pp. 980-986, May 2005.

K. Kim, K. K. Das, R V. Joshi, and c.-T. Chuang, "Leakage power analysis of 25-nm double-gate CMOS devices and circuits," IEEE Trans. Electron Devices, vol. 52, no. 5, pp. 980-986, May 2005.

Shin'ichiro Mutoh, TakakuniDouseki, Yasuyuki Matsuya, Takahiro Aoki, Satoshi Shigematsu, and Junzo Yamada [Members IEEE], "I-V Power Supply High-Speed Digital Circuit Technology with Multi-threshold-Voltage CMOS," IEEE journal of solid-state circuits, pp. 847-854, August 1995.

Downloads

Published

How to Cite

Issue

Section

License

This work is licensed under a Creative Commons Attribution-ShareAlike 4.0 International License.

All papers should be submitted electronically. All submitted manuscripts must be original work that is not under submission at another journal or under consideration for publication in another form, such as a monograph or chapter of a book. Authors of submitted papers are obligated not to submit their paper for publication elsewhere until an editorial decision is rendered on their submission. Further, authors of accepted papers are prohibited from publishing the results in other publications that appear before the paper is published in the Journal unless they receive approval for doing so from the Editor-In-Chief.

IJISAE open access articles are licensed under a Creative Commons Attribution-ShareAlike 4.0 International License. This license lets the audience to give appropriate credit, provide a link to the license, and indicate if changes were made and if they remix, transform, or build upon the material, they must distribute contributions under the same license as the original.