An Efficient FPGA-Based Dynamic Partial Reconfigurable Implementation

Keywords:

Fault Tolerant System, Generic Controller, Partial Reconfiguration, Triple Modular RedundancyAbstract

Today's system developers can choose from many electronic gadgets. There are simple integrated circuits, programmable microcontrollers, bespoke chips, and more complex logic devices on the market. FPGA technology is famous for rapid prototyping and implementing small-unit systems. They offer high logic density and the ability to readily upgrade established designs to meet new standards or change system function or structure. FPGAs have a shorter design cycle than custom devices and can use low-cost design tools. These benefits reduce FPGA design NRE. Their weakness is radiation [1]. This primarily involves SRAM-based FPGAs, which are in high demand because they have high throughput at a low cost. The design of fault-tolerant systems can reduce the number of errors they experience.

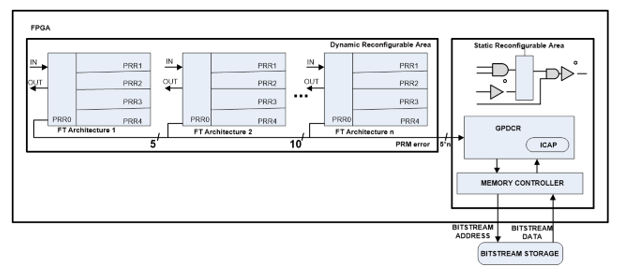

A fault-tolerant FPGA design approach is presented as a proposal in this study. This technique can be utilized in systems with a constrained redundancy area and cannot use excess resources while operational. In order to alleviate some of the issues with the system, we will implement FPGA partial dynamic reconfiguration. This technique's primary focus is recovery from both temporary and permanent flaws. SEU faults will be simulated via errors in the FPGA configuration memory. After the job, an analysis of the solution's hardware overhead and the effectiveness of the secured system design is carried out.

Downloads

References

M. Wirthlin, E. Johnson, N. Rollins, M. Caffrey, and P. Graham. The reliability of FPGA circuit designs in the presence of radiation-induced configuration upsets. In Field-Programmable Custom Computing Machines, 2003. FCCM 2003. 11th Annual IEEE Symposium on, pages 133-142, 2003.

Flynet E., Yuffie M. and Knoll E. 4.1 14nm 6th-generation core processor soc with low power consumption and improved performance. In 2016 IEEE International Solid-State Circuits Conference, ISSCC 2016, San Francisco, CA, USA, January 31 - February 4, 2016, pages 72-73, 2016.

Patrick Blau. Juno: Spacecraft information. URL: <http://spaceflight101.com/juno/spacecraft-information/>. Accessed: 2016-07-06.

John Rhea. Bae systems move into third-generation rad-hard processors. Military & Aerospace Electronics, 13(5), 2002.

Aiwu Ruan, Bairui Jie, Li Wan, Junhao Yang, Chuanyin Xiang, Zujian Zhu, and Yu Wang. A bitstream readback-based automatic functional test and diagnosis method for Xilinx FPGAs. Microelectronics Reliability, 54(8):1627-1635, 2014.

Conrado Pilotto, Jose Rodrigo Azambuja, and Fernanda Lima Kastensmidt. They synchronize triple modular redundant designs in dynamic partial reconfiguration applications. In SBCCI '08: Proceedings of the 21st annual symposium on Integrated circuits and system design, pages 199-204, New York, NY, USA, 2008. ACM.

Yoshihiro Ichinomiya, Shiro Tanoue, Motoki Amagasaki, Masahiro Iida, Morihiro Kuga, and Toshinori Sueyoshi. Improving the robustness of a softcore processor against us by using tmr and partial Reconfiguration. In Proceedings of the 2010 18th IEEE Annual International Symposium on Field-Programmable Custom Computing Machines, FCCM '10, pages 47-54, Washington, DC, USA, 2010. IEEE Computer Society.

Jason A. Cheatham, John M. Emmert, and Stan Baumgart. A survey of fault-tolerant methodologies for FPGAs. ACM Trans. Des. Autom. Electron. Syst., 11(2):501-533, 2006.

Miculka L. and Kotasek Z. Synchronization technique for tmr system after dynamic Reconfiguration on FPGA. In The Second Workshop on Manufacturable and Dependable Multicore Architectures at Nanoscale (MEDIAN 2013), pages 53-56. Politecnico di Milano, 2013.

M. Straka, J. Kastil, and Z. Kotasek. Generic partial dynamic reconfiguration controller for fault-tolerant designs based on FPGA. In NORCHIP '10, pages 1-4, Washington, DC, USA, 2010. IEEE CS.

Straka M., Miculka L., Kastil J. and Kotasek Z. Test platform for fault tolerant systems design qualities verification. In 15th IEEE International Symposium on Design and Diagnostics of Electronic Circuits and Systems pages 336-341. IEEE Computer Society, 2012.

Miculka L. and Kotasek Z. Generic partial dynamic reconfiguration controller for transient and permanent fault mitigation in fault tolerant systems implemented into FPGA. In 17th IEEE Symposium on Design and Diagnostics of Electronic Circuits and Systems, pages 171-174. IEEE Computer Society, 2014.

Downloads

Published

How to Cite

Issue

Section

License

This work is licensed under a Creative Commons Attribution-ShareAlike 4.0 International License.

All papers should be submitted electronically. All submitted manuscripts must be original work that is not under submission at another journal or under consideration for publication in another form, such as a monograph or chapter of a book. Authors of submitted papers are obligated not to submit their paper for publication elsewhere until an editorial decision is rendered on their submission. Further, authors of accepted papers are prohibited from publishing the results in other publications that appear before the paper is published in the Journal unless they receive approval for doing so from the Editor-In-Chief.

IJISAE open access articles are licensed under a Creative Commons Attribution-ShareAlike 4.0 International License. This license lets the audience to give appropriate credit, provide a link to the license, and indicate if changes were made and if they remix, transform, or build upon the material, they must distribute contributions under the same license as the original.