A MILP based Optimization and FPGA Implementation of Efficient Polyphase Multirate Filters

Keywords:

Polyphase Structure, MILP, Power consumption, Logic area, system generator, Computation rate, ThroughputAbstract

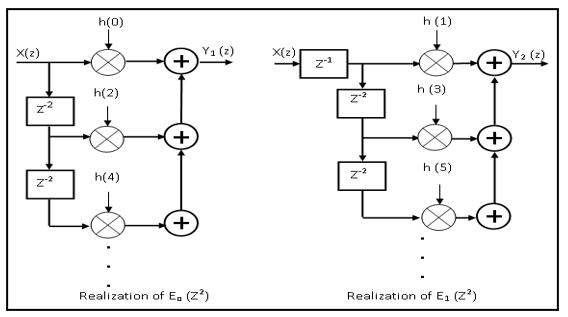

Effectively implementing digital filters at cheap cost is made possible by the DSP field's multirate filtering method. By taking advantage of concurrency in multirate digital filters, the processing burden of polyphase decomposition techniques is reduced. Since each positive bit requires an extra adder in circuitry execution and more toggling at the end of CMOS circuits, reducing the number of positive terms in the filter coefficients is a primary focus of filter improvement. In order to lessen the quantity of nonzero factors in the filter coefficients, an innovative method is proposed in this article. Polyphase shapes are used to test the suggested algorithm's effects on power usage. The constructions are manufactured for Spartan6 xc6slx150T-4fgg676 FPGA panel consuming system generator for obtaining the other performance indices like throughput, speed, logic area and computation rate. In spite of occupying more area, efficient polyphase decimator structure is found to be superior to the polyphase and decimation structures.

Downloads

References

H. Johansson and L. Wanhammar, “Filter Structures Composed of All-Pass and FIR Filters for Interpolation and Decimation by a Factor of Two,” IEEE Trans. On Circuits and Systems-II: Analog and Digital Signal Processing, vol. 46, no.7, pp. 896–905, July 1999.

ShahriarEmami, “New Methods for Computing Interpolation and Decimation Using Polyphase Decomposition,” IEEE Trans. On Education, vol.42, no.4, pp.311–314, Nov. 1999.

Kai-Yuan Cheng, “Multiplierless Multirate FIR Digital Filter /Decimator / Interpolator Module Generator,” National Central University Jhongli 320, Taiwan, R.O.C., 2003.

M. B. Yeary, W. Zhang, J. Q. Trelewicz, Y. Zhai and B. McGuire, “Theory and Implementation of a Computationally Efficient Decimation Filter for Power-Aware Embedded Systems,” IEEE Trans. Instru. Meast., 55(5), pp-1839–1849,2006.

N. Onwuchekwa, G.A. Chukwudebe, “Implementation Of Computationally Efficient Algorithms for Multirate Digital Signal Processing Systems,” Afr. Journal of Comp. & ICT, vol. 1, no. 1, pp. 33 – 45, 2008.

Ahmed Shahein, Qiang Zhang, NiklasLotze, and YiannosManoli, “A Novel Hybrid Monotonic Local Search Algorithm for FIR Filter Coefficients Optimization,” IEEE Trans. on Circuits and Systems—I: Regular Papers, vol. 59, no. 3, March 2012.

N. Younis, M. Ashour, and A. Nassar, “Power-Efficient Clock/Data Distribution Technique for Polyphase Comb Filter in Digital Receivers,” IEEE Trans. Circuits Syst. II, Express Briefs, 56(8), pp-639–643, 2009.

Dr.K.B.Khanchandani, Kundan Kumar, “Design and Implementation of Custom Low Power DSP blocks for Biomedical Applications,” Int. Journal of Advanced Engineering & Application, 2011.

M. Madheswaran and V. Jayaprakasan, “Implementation And Comparison Of Different CIC Filter Structure For Decimation,” ICTACT Journal On Communication Technology, 4(2), pp-709–716, 2013.

V. Jayaprakasan and M. Madheswaran, “FPGA Implementation of FIR based Decimation Filter Structure for WiMAX Application,” International Journal of Advanced Research in Computer and Communication Engg., vol. 2, pp. 2830–2837,2013.

P. Jacob and Mr. Anoop B.N, “Design and Implementation of Polyphase Decimation Filter,” International Journal of Computer Networks and Wireless Communications (IRACST), vol. 4, no. 2, pp. 123–127, April 2014.

Rajendra M. Rewatkar, Dr. Sanjay L. Badjate, “Optimization of Multirate Polyphase Decimator using MCM and Digit Serial Architecture,” International Journal of Computer Science and Information Technologies, vol. 5, 2014.

Robert D. Turney, Chris Dick, and Ali M. Reza, “Multirate Filters and Wavelets: From Theory to Implementation”, Xilinx Inc., San Jose, CA 95124, USA.

E. Ifeachor and B. W. Jervis, Digital Signal Processing. 2nd ed. India: Pearson, 2011.

D.M. Kodek, “Design of Optimal Finite Wordlength FIR Digital Filters Using Integer Programming Techniques,” IEEE Trans. On Acoustics, Speech, and Signal Processing, vol. ASSP-28,no. 3, pp. 304–308, June 1980.

[16]Y.C. Lim, R. Yang, D.N. Li, J.J. Song, “Signed Power-of-Two Term Allocation Scheme for the Design of Digital Filters,” IEEE Trans. on Circuits and Systems-II: Analog and Digital Signal Processing, vol.46, no.5, pp. 577–584, May 1999.

O. Gustafsson, L. Wanhammar, “Design of Linear-Phase FIR Filters Combining Subexpression Sharing with MILP,” in Proceedings of 45th Midwest symposium on Circuits and Systems (MWSCAS’02), vol. 3, pp. 9–12, Aug. 4-7, 2002.

Y.C. LIM, “Design of Discrete-Coefficient-Value Linear Phase FIR Filters With optimum Normalized Peak Ripple Magnitude,” IEEE Trans. on Circuits and Systems, vol. 37, no.12, pp.1480-1486, Dec. 1990.

Chao-Liang Chen, Michael C. Chen, Alan N. Willson Jr, “A Trellis Search Algorithm for the Design of FIR Filters with Signed-Powers-of-Two Coefficients,” in Proceedings of IEEE Midwest symposium on Circuits and Systems, Ames, IA,pp.619-622, Aug. 18-21,1996.

Stefano Traferro, FulvioCapparelli, Francesco Piazza and Aurelio Uncini, “Efficient Allocation Of Power-of-Two Terms In FIR Digital Filter Design Using Tabu Search,” in Proceedings of IEEE International symposium on Circuits and Systems (ISCAS’99), Orlando, FL, vol.3, pp.411-414, May 30- June 02, 1999

Chia. Yu Ya, “A Study of SPT-term distribution of CSD numbers and its application for designing fixed-point linear phase FIR filters,” in Proceedings of IEEE International symposium on Circuits and Systems (ISCAS’01), vol.2, pp.301-304, 2001.

Tetsuya Fujie Rika Ito Kenji SuyamaRyuichiHirabyashi, “A new heuristic signed-power of two term allocation approach for designing of FIR filters,” in Proceedings of IEEE International symposium on Circuits and Systems (ISCAS’03) , vol. 4, pp.285-288, May 25-28, 2003.

Oscar Gustafsson, Håkan Johansson, and Lars Wanhammar, “An MILP Approach for the Design of Linear-Phase FIR Filters with Minimum Number of Signed-Power-of-Two Terms,” in Proceedings of European Conference on Circuit Theory Design, Espoo, Finland, 2001.

W.S. Lu and T. Hinamoto, “ Design of FIR filters with Discrete Coefficients via Polynomial Programming: Towards the Global Solution,” in Proceedings of IEEE International symposium on Circuits and Systems (ISCAS’07),New Orleans, LA, pp. 2048-2051, May 27-30, 2007.

W.S. Lu, “Design of FIR filters with Discrete coefficients: a Semidefinite Programming Relaxation Approach,” in Proceedings of IEEE International Symposium on Circuits and Systems (ISCAS’01), Sydney, NSW, vol. 2, pp. 297-300, May 6-9, 2001.

Z. Ye and C.-H. Chang, “Local search method for FIR filter coefficients synthesis,” in Proceedings of IEEE International Workshop on Electronic Design, Test and Appllications (2nd DELTA’04), pp. 255–260, 2004.

Roger Woods, John McAllister, Y. Yi and G. Lightbody, FPGA-based Implementation of Signal Processing Systems. John Wiley and Sons, 2008.

Sami Kadhim Hasan, “FPGA Implementations for Parallel Multidimensional Filtering Algorithms,” Ph.D Thesis, Agriculture and Engineering Newcastle University, June 2013.

Downloads

Published

How to Cite

Issue

Section

License

This work is licensed under a Creative Commons Attribution-ShareAlike 4.0 International License.

All papers should be submitted electronically. All submitted manuscripts must be original work that is not under submission at another journal or under consideration for publication in another form, such as a monograph or chapter of a book. Authors of submitted papers are obligated not to submit their paper for publication elsewhere until an editorial decision is rendered on their submission. Further, authors of accepted papers are prohibited from publishing the results in other publications that appear before the paper is published in the Journal unless they receive approval for doing so from the Editor-In-Chief.

IJISAE open access articles are licensed under a Creative Commons Attribution-ShareAlike 4.0 International License. This license lets the audience to give appropriate credit, provide a link to the license, and indicate if changes were made and if they remix, transform, or build upon the material, they must distribute contributions under the same license as the original.